# A Rule-based Method for Minimizing Power Dissipation by Reducing Switching Activity of Digital Circuits

#### Subrata Das

Dept. of Information Technology

Academy of Technology

Hooghly (Aedconagar), West Bengal, 712121, India

dsubrata.mt@gmail.com

### **Sudip Ghosh**

School of VLSI Technology

Indian Institute of Engineering Science & Technology (IIEST)

Howrah, West Bengal, 711103, India,

sudip.ghosh@vlsi.iiests.ac.in

Parthasarathi Dasgupta Management Information System Group Indian Institute of Management Calcutta, Kolkata Diamond Harbour Rd, Joka, Kolkata, West Bengal 700104, India <u>partha@iimcal.ac.in</u>

Samar Sensarma Department of Computer Science & Engineering University of Calcutta, Kolkata 92, A.P.C. Road, Kolkata - 700 009, West Bengal, India sssarma2010@gmail.com

# A Rule-based Method for Minimizing Power Dissipation by Reducing Switching Activity of Digital Circuits

Subrata Das, Sudip Ghosh, Parthasarathi Dasgupta and Samar Sensarma

A sr c — Minimization of power dissipation of VLSI circuits is one of the major concerns of recent digital circuit design primarily due to the ever decreasing feature sizes of circuits, higher clock frequencies and larger die sizes. The primary contributors to power dissipation in digital circuits include leakage power; short-circuit power, and switching power. Of these, power dissipation due to circuit switching activity constitutes the major component. As such, an effective mechanism to minimize power loss in such cases often involves the minimization of switching activity. In this paper, we propose an intelligent rule-based algorithm for reducing the switching activity of digital circuits at logic optimization stage. The proposed algorithm is empirically tested for several standard digital circuits with Synopsis EDA tool and results obtained are quite encouraging.

*ey ords* — Switching Activity, low-power VLSI circuits, CMOS, Power dissipation, dynamic power, electromigration.

#### **1** INTRODUCTION

Traditionally, the major concerns of the VLSI designers include minimization of chip area, enhancement of performance, testability, reduction of manufacturing cost and improvement of reliability. With increasing use of portable devices and wireless communication systems, reduction of energy consumption and hence reduction of power dissipation and optimization of chip temperature have become some recent major concerns in VLSI design [17]. Power dissipated by a digital system increases the temperature of the chip and affects battery life of the digital devices [14]. Aggressive device scaling also causes excessive increase in power per unit area of the chip. This high power dissipation in VLSI devices is usually manifested in the form of rise of chip temperature. As such, heat generation and its removal from a chip are of serious concern [2]. The heat removal system must be efficient and must keep the junctions below a certain threshold, as determined by reliability constraints. With higher level of integration more and more transistors are being packed into smaller areas. Thus, for high level of integration, heat removal is a dominant design factor. In absence of appropriate removal of the generated heat, the chip temperature may rise causing thermal breakdown. One of the major reasons of VLSI chip failure is due to interconnect failure, often attributed to the phenomenon of electromigration, causing leakage power. The mean time to failure (MTTF) of interconnect due to electromigration is given by Black's equation [7]

$$MTTF \quad Aj^{-2}e^{\left(\frac{Q}{KT}\right)} \tag{1}$$

where A is a constant based on the iven (37()]TJ - o(n) - 0.25716(j) - 278] Biton to

ece(ndu gioie -30.1643(()2.804er

resistance of the transistors consumes electrical e

is presented in [8] using the general delay model. An analytical approach to compute the switching activity of digital circuits at word-level in the presence of glitches and correlation is presented in [16]. The work in [5] provides an interesting repository of recent techniques of power modeling and low power design based on high-level synthesis. The evaluation and reduction of switching activity in combinational logic circuits considering both the transitions  $1 \rightarrow 0$  and  $0 \rightarrow 1$  at any output node is proposed in [15]. In order to satisfy the classical probabilistic approach that limits the maximum value of switching activity to 1 the definition of switching activity as proposed in [15] was customized in [19]. An algorithmic approach at the Gate level using k-map

$$P_1 = \frac{|N_i|}{|N_i| + |X_i|} \tag{4}$$

**Def n** on For a given node of a circuit the probability of transition either from 0 to 1 or from 1 to 0 is known as switching activity (SA) of that node.

Thus, switching activity of node *i* is given by the composite probability

$$SA \quad P_0 \quad P_1 \quad \frac{|N_i| \quad |X_i|}{[|N_i| + |X_i|]^2} \tag{5}$$

For instance the switching activity of 2-input AND Gate (|Ni| = 1 and |Xi| = 3) is given by  $\frac{3}{16}$  and this contributes to the dynamic power loss of the AND Gate.

As already mentioned, power dissipation in digital circuits can be reduced by minimizing its total switching activity. In order to minimize the switching activity one must know the minimum and maximum values of switching activity for the logical expression for a particular switching circuit. The total numbers of values (0's and 1's) in the output column of a truth table are dependent solely on the number of inputs and thus may be considered to be invariant for a given

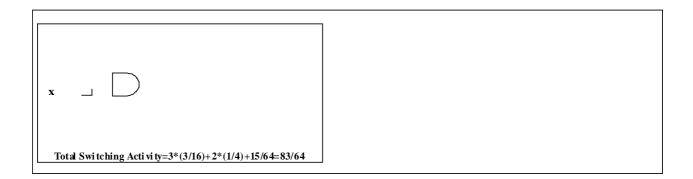

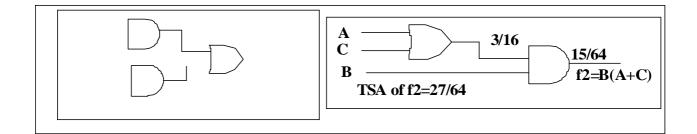

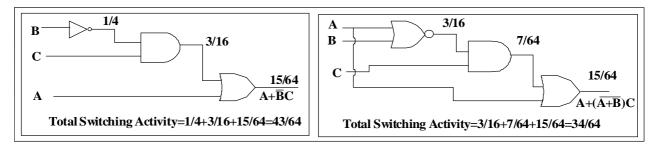

Consider a logical expression  $f = a\overline{b}c + \overline{ab} + \overline{c+d}$ . The switching activity for  $f1 = a\overline{b}c$  is  $\frac{7}{64}$ . This is due to the fact that the output is 1 only for the input vector 101. As such, the number of 1's and 0's in the output column are respectively 1 and 7. For the implementation of  $f1 = a\overline{b}c$ , a NOT Gate is required for  $\overline{b}$ , having switching activity  $\frac{1}{4}$ , an AND gate is required for ac with switching activity  $\frac{3}{16}$ . The outputs of these NOT Gate and AND Gate are inputs to a second AND Gate having switching activity  $=\frac{7}{64}$ . The total switching activity for f1 is thus  $\frac{1}{4} + \frac{3}{16} + \frac{7}{64}$ .

Clearly, the switching activities for both  $f_2$  ab and  $f_3$   $\overline{c+d} \operatorname{are} \frac{3}{16}$ . When represented as a minterm, the function is given by f 0,1,2,3,4,5,6,7,8,9,10,11,12 and the activity is  $\frac{39}{256}$  (as |Ni|=3,|Xi|=13). Thus, the total switching activity of the circuit is  $\frac{1}{4} + \frac{3}{16} + \frac{7}{64} + \frac{7}{64} + \frac{3}{16} + \frac{39}{256} + \frac{303}{256}$  (Figure 1).

#### **4 MOTIVATION OF THE WORK**

According to International Technology Roadmap for Semiconductor (ITRS) one of the major goals of the semiconductor industry is to be able to continue to scale the technology in overall performance. The performance of the components and the final chip can be measured in many logical expression of the switching functions. Logic optimization is often achieved using the standard SOP or POS expression. However, the focus of earlier works in logic optimization is primarily on the reduction of number of input terms or number of literals [6]. An algorithm for interconnection-aware two-level logic optimization of multi-output SOP functions appears in

*O ser on* If a sum-of-product expression contains pair-wise common Boolean literals with multiplication distributed over addition like  $f1 \quad A.B + B.C$  then modification of this expression applying converse distributive property i.e.  $f1 \quad A.B + B.C \quad f2 \quad B.(A + C)$  reduces the number of gates as well as switching activity. Figure 5 shows the reduction of switching activity du6224.67 m (s)

2-variable Boolean expressions according to Lemma 2. This Lemma 2 can be effectively used to reduce the switching activity if the number of complemented term is odd. Hence this Lemma 2 can be applied in the proposed method described in this paper if  $n \ge 2$  and n is even.

Le : For an

O ser on

For n=2,  $t_2 = \frac{1}{2^2} = \frac{1}{2^4} = \frac{1}{4} = \frac{1}{64} = \frac{3}{16} = \frac{1}{4}$ . Let us assume that the results holds for n=k variables. i.e.  $t_k = \frac{1}{2^k} = \frac{1}{2^{2k}} = \frac{1}{4}$ . Now we need to show that the result also holds for n = k + 1 variables.  $t_{(k+1)} = \frac{1}{2^{(k+1)}} = \frac{1}{2^{2(k+1)}} = \frac{1}{2} [\frac{1}{2^k} = \frac{1}{2^{2k}}] = \frac{1}{2^{(2k+1)}} = \frac{1}{2} t_k = \frac{1}{2^{(2k+1)}} = \frac{1}{4}$

$\Box$

*Le* If a product term in a logical expression contains odd number of complemented literals, then switching activity can be reduced by replacing pair of complemented literals with their NOR combination and replacing remaining one complemented literal  $\overline{x_i}$  by  $x_i$  1. And if product term contains only one complemented literal  $\overline{x_i}$  then switching activity can be reduced by replacing complemented literal  $\overline{x_i}$  by  $x_i$  1.

#### Proof [By Induction]

We consider a product term in a logical expression containing two literals of the form  $x\overline{y}$ . From Figure 17a and Figure 17c it is evident that the switching activity for  $\overline{y}$  is  $\frac{1}{4}$  and that of for  $x\overline{y}$  is  $\frac{3}{16}$ . Thus, the total switching activity in this case is given by

$$TSA_2 1c \quad \frac{1}{4} + \frac{3}{16} \quad \frac{7}{16}$$

(8)

( $TSA_i jc$  represents Total Switching Activity of a product term containing i number of literals out of which j number of literals are in complemented form and  $TSA_i jm$  represents the same of a modified product term.)

Now the expression  $x\overline{y}$  can be modified as  $x(y \ 1) \ xy \ x$ . Corresponding truth table and circuit diagram are shown in Figure 17c and Figure 17b respectively.

From Figure 17c and Figure 17b the switching activity for xy is  $\frac{3}{16}$  and that of for xy x is  $\frac{3}{16}$ . So total switching activity in this case

$$TSA_2 1m \quad \frac{3}{16} + \frac{3}{16} \quad \frac{6}{16}$$

(9)

Thus, from the equations 12 and 13 it is clear that  $TSA_3 3m$   $TSA_3 3c$ . Thus, product terms containing 2 and 3 literals with odd number of comp

## Algorithm Minimize Switching Activity ()

Input: Truth Table

Output: Function for minimal switching activity

- 1. Obtain the minimal Sum-of-Product  $(f_{SOP})$  or Product-of-Sum  $(f_{POS})$  expression using any standard method for the minimization of given switching function f.

- 2. Apply Rule 1 and Rule 2 to reduce the switching activity

- 3. If either the  $(f_{SOP})$  or  $(f_{POS})$  does not contain any complemented variable then

- Calculate the total switching activity of the function corresponding to  $(f_{SOP})$  or  $(f_{POS})$ .

- 4. Take the function with minimum switching activity.

- 5. Endif

- 6. If the product term in  $f_{SOP}$  contains even number of complemented terms then

- Replace a pair of complemented terms by their corresponding NOR combination using De' Morgan's theorem (Rule 3).

- 8. Endif

- 9. If the sum term in  $f_{POS}$  contains even number of complemented terms then

- 10. Replace a pair of complemented terms by NAND Gate using De, Morgan's theorem (Rule 3).

- 11. Endif

- 12. If applicable then

- 13. Apply Rule 4, Rule 6, Rule 7, Rule 9, Rule 10, and Rule 11 to reduce the switching activity.

14. Endif

- 15. If a  $f_{SOP}$  ( $f_{POS}$ ) contains only one complemented term  $x_i$  then

- 16. Apply Rule 8 or Rule 12 (in case of SOP) from lyf-26 Tm994()]TJ -257.553 -20.64 7d [(1)-3.58076(6

#### **8** EXPERIMENTAL RESULTS

The proposed rule-based algorithm is implemented in Xilinx 14.7 and power estimation has done using Synopsys EDA tool -DESIGN VISION version I-2013.12-SP1, 20, 2014 under CENT OS and using TSMC 120 nm library.

Without loss of generality, for our simulations, we consider only 2-input logic gates. The switching activity of some basic circuits and the associated dynamic power dissipation using conventional SOP (POS) method and our proposed method are summarized in Table 4.

We observe that the total number of switching activity for our proposed method never exceeds, and is less in most of the cases than those obtained using the traditional logic optimization.

#### Co p r son of o r proposed e hod h he e s ng e hod of [20]

Reduction of switching activity and hence power dissipation of VLSI CMOS circuits by our proposed algorithm is applicable for any number of input variables and any kind of circuits. In [20] the authors basically modify the k-map to reduce the switching activity. Logic optimization using k-map is limited to 6 variables. Moreover, th

designed using rule-based algorithm proposed in this paper is interestingly applicable for any number of variables. Experimental results show over 34% reduction of switching activity. The works presented in this paper can be further improved by considering both delay and power as objective functions.

#### REFERENCES

[1] K. Roy, S. C. Prasad, Low Power CMOS VLSI Circuit Design, Wiley India Ed (2011).

[2] P Ghosal, T Samanta, H Rahaman, P Dasgupta, "Thermal-aware placement of standard cells and gate arrays: Studies and observations" IEEE Computer Society Annual Symposium on VLSI, ISVLSI'08.(2008), pp 369-374.

[3] N. A. Sherwani, "Algorithms for VLSI Physical Design Automation" Springer, 3<sup>rd</sup> Ed(2008).

[4] N.Wehn and M. Munch, "Minimising power consumption in digital circuits and systems: An

[16] J. H. Satyanarayana and K. K. Parhi, "Theoretical Analysis of Word-Level Switching Activity in the Presence of Glitching and Correlation" IEEE Transactions on VLSI, Vol. 8, No. 2. pp. 148-159.

[17] S. Chattopadhyay, N. Choudhary,: "Genetic Algorithm based Approach for Low Power Combinational Circuit Testing " Proceedings of the 16th International conference on VLSI Design(VLSI'03).

[18] S. Koziel, W. Szczesniak,: "Reducing Average and peak temparatures of VLSI CMOS circuits by means of evolutionary algorithm applied to high level systhesis", Microelectronics

## **Figures and Tables**

Figure 1. Switching Activity for  $a\overline{b}c + \overline{ab} + \overline{c+d}$

Figure 9: Switching Activity for  $A + \overline{B}C$  and  $A + (\overline{A+B})C$

| <br>>~ | $\square$ |  |  |

|--------|-----------|--|--|

|        |           |  |  |

|        |           |  |  |

| A | В | $\overline{A}$ | $\overline{A+B}$ | AB | $\overline{A} + AB$ | $\overline{A+B}+B$ |

|---|---|----------------|------------------|----|---------------------|--------------------|

| 0 | 0 | 1              | 1                | 0  | 1                   | 1                  |

| 0 | 1 | 1              | 0                | 0  | 1                   | 1                  |

| 1 | 0 | 0              | 0                | 0  | 0                   | 0                  |

| 1 | 1 | 0              | 0                | 1  | 1                   | 1                  |

Table 2: Truth table for  $\overline{A} + AB$  and  $\overline{A + B} + B$

1